5.1.0 实验介绍

实验简介

本教程以实验为主,结合相应的实验案例,以详细的讲解和实验步骤让大家尽快熟悉FPGA开发的基本流程、Ridiant软件平台的使用方法以及本节实验相关模块的工作原理。

- 熟悉和掌握FPGA开发的基本流程

- 掌握Ridiant软件平台的基本使用方法

- 了解使用SigmaDelta ADC的原理

- 掌握使用Verilog HDL语言基于FPGA实现ADC数字电压表的原理及实现方法

背景知识

多数FPGA芯片上没有ADC的功能,而一些应用则需要用到ADC对一些模拟信号,比如直流电压等进行量化,有没有特别简单、低成本的实现方法呢?

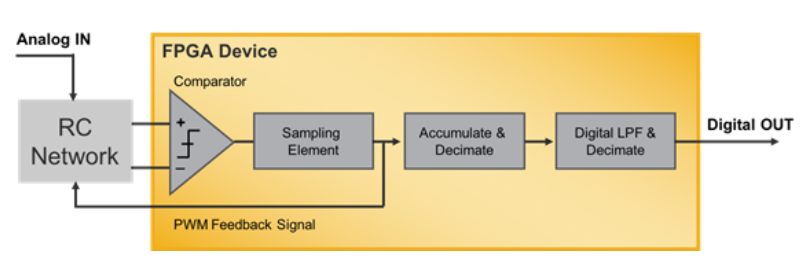

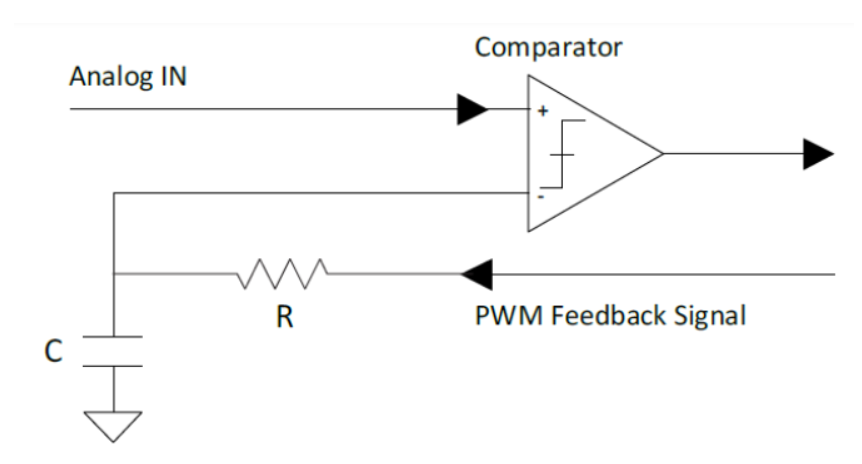

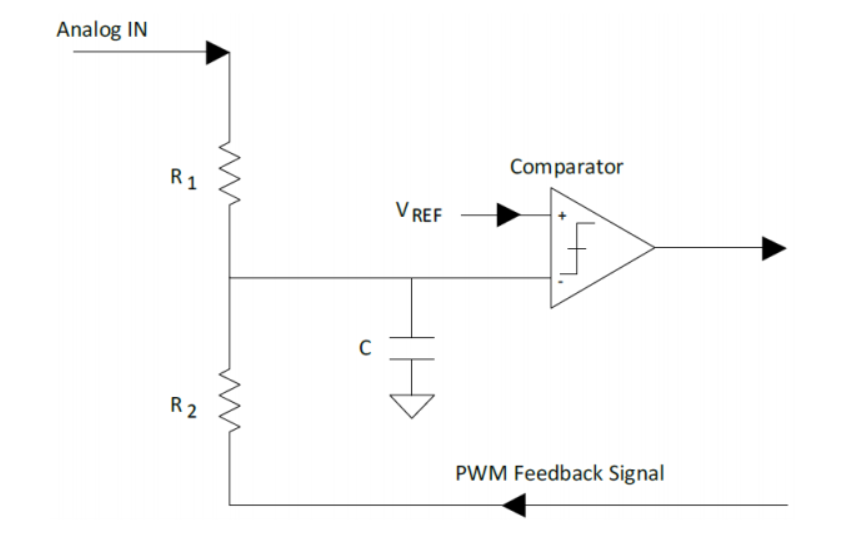

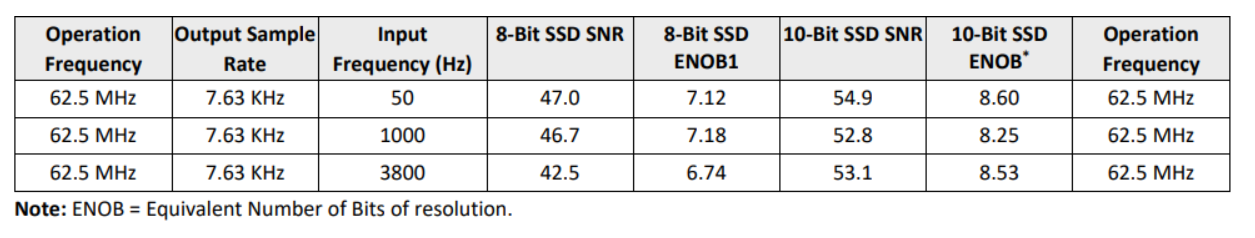

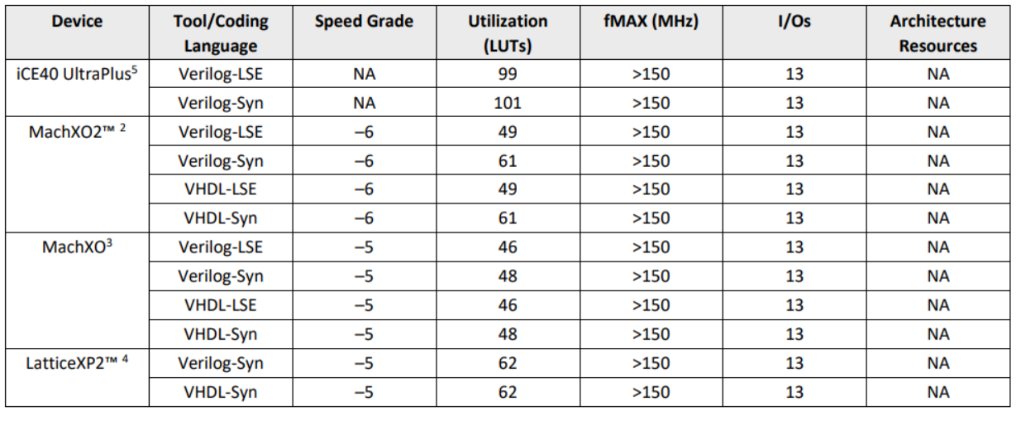

在要求转换速率不高的情况下,完全可以借助一颗高速比较器(成本只有几毛钱)来实现对模拟信号的量化,Lattice的官网上一篇文章就介绍了如何制作一个简易的Sigma Delta ADC,如果FPGA能够提供LVDS的接口,连外部的高速比较器都可以省掉。由于我们的小脚丫FPGA核心模块在设计的时候没有考虑到LVDS的应用场景,所以还是需要搭配一个高速的比较器来实现Lattice官网上推荐的简易Sigma Delta ADC的功能。

工作原理:

实验环境

- 硬件环境:STEP FPGA 实验平台

- 软件环境:Ridiant开发环境